27 апреля, 22:42

TSMC анонсирует процессоры с 40-кратным приростом производительности к 2027 году

DNS_Club

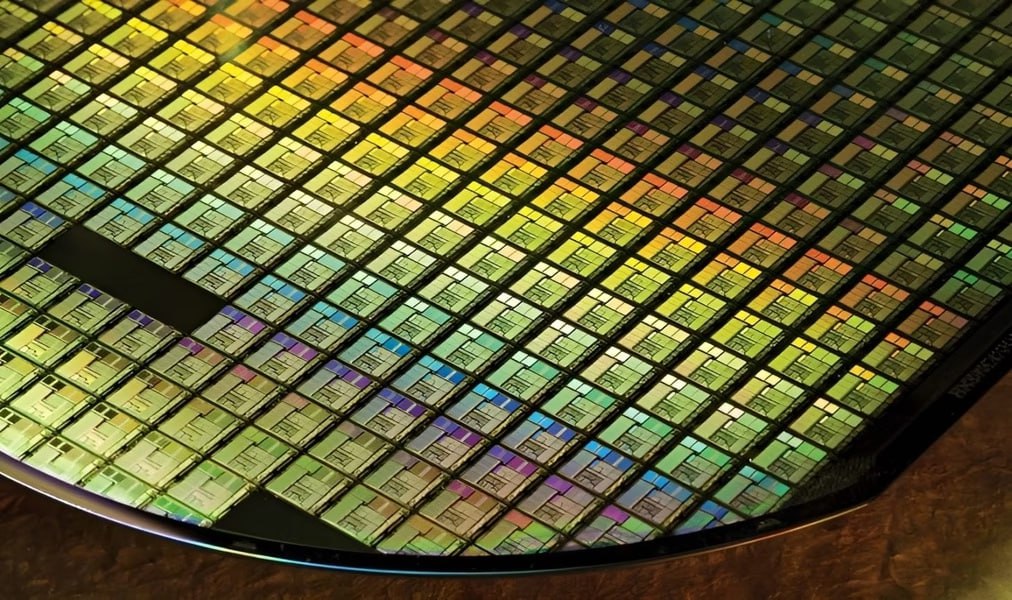

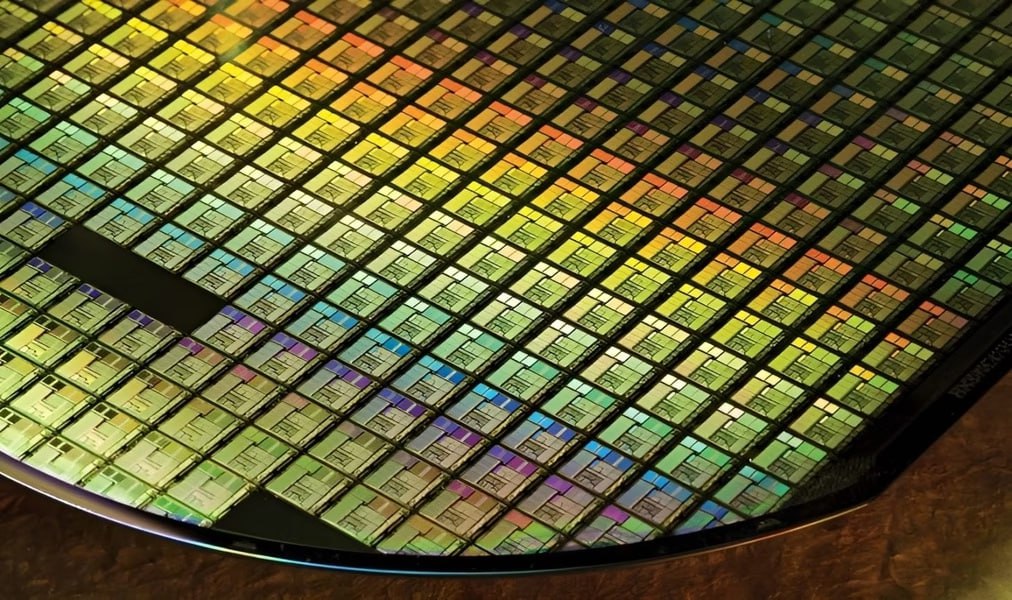

TSMC разрабатывает процессоры на 1000 Вт с 40-кратным приростом производительности TSMC анонсировала новое поколение упаковки CoWoS, которое позволит создавать гигантские многочиповые серверные процессоры площадью до 7885 мм2 на подложках 120 × 150 мм. Такие решения обеспечат прирост производительности до 40 раз по сравнению с традиционными чипами. Читать далее

Новости IT | Мир Программиста

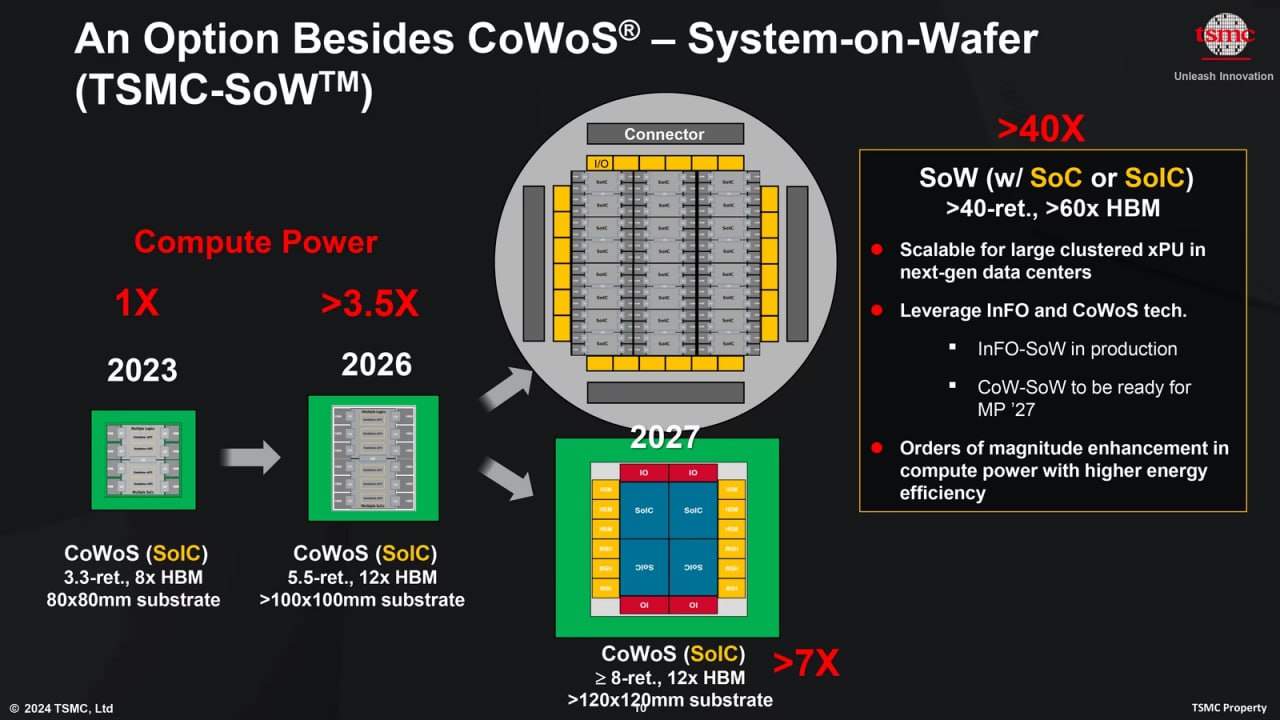

TSMC представила прорыв: чипы станут в 40 раз мощнее. Intel и Samsung не успевают TSMC придумала технологию SoW-X: — Увеличивает мощность в 40 раз против нынешних моделей. — Позволяет ставить 60 блоков сверхбыстрой памяти HBM — как 60 спортивных двигателей в одном авто. — Запуск производства — 2027 год. До этого TSMC использовала технологию CoWoS: у неё 9.5x площадь, 12 блоков HBM. У SoW-X: 40x площадь + 60 HBM.

Программист * Все о компьютерах

TSMC представила прорыв: чипы станут в 40 раз мощнее. Intel и Samsung не успевают TSMC придумала технологию SoW-X: — Увеличивает мощность в 40 раз против нынешних моделей. — Позволяет ставить 60 блоков сверхбыстрой памяти HBM — как 60 спортивных двигателей в одном авто. — Запуск производства — 2027 год. До этого TSMC использовала технологию CoWoS: у неё 9.5x площадь, 12 блоков HBM. У SoW-X: 40x площадь + 60 HBM.

RUSmicro

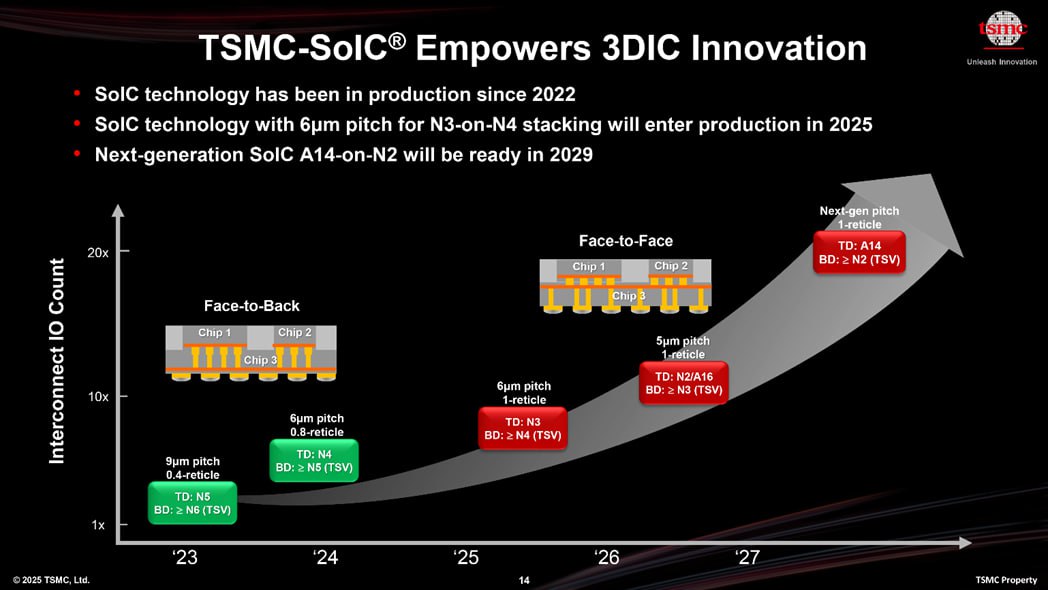

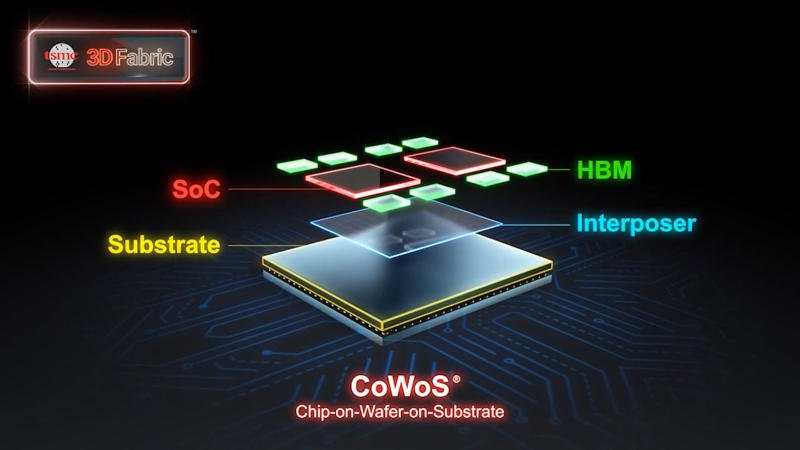

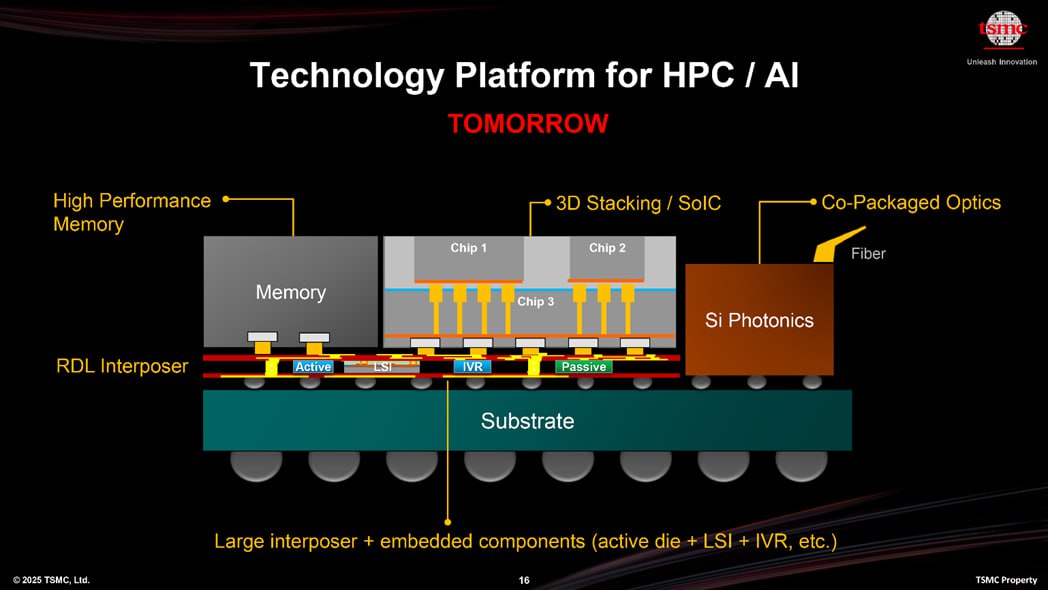

2 Пока что решения CoWoS TSMC позволяют работать с интерпозерами до 2831 кв мм., что примерно в 3.3 раза больше, чем предельный размер сетки фотошаблона компании у TSMC это 830 кв.мм . По этой технологии пакуются ускорители AMD Instinct MI300X и графические процессоры Nvidia B200, объединяющие 2 больших цифровых чипа и 8 стеков памяти HBM3 или HBM3E. Но этого мало для приложений ближайшего будущего. В 2026-2027 году в TSMC готовятся к переходу на CoWoS-L с поддержкой интерпозеров до 4719 кв.мм, что в 5.5 раз больше стандартной площади сетки. В такой упаковке поместится до 12 стеков памяти, что потребует подложки размером 100х100 10 тыс кв мм . От соответствующей микросхемы ожидается вычислительная способность в 3.5 раза выше, чем от текущей. Этого может быть достаточно для процессоров Nvidia Rubin с 12 стеками HBM4. На этом на Тайване останавливаться не планируют, собираясь ввести интерпозеры с площадью до 7.885 тыс. кв. мм на подложках размером 120х150 мм это больше чем футляр для компакт-диска 142х125 мм . Такое изделие уже трудно назвать «микросхемой». Ожидается, что это позволит разместить четыре 3D-стекированных системы-на-интегрированных чипах SoIC . Например, это может быть кристалл N2/A16, лежащий поверх цифрового кристалла N3, дюжина стеков памяти HBM4 и дополнительные кристаллы ввода вывода I/O Die . ..

АРПЭ

Размеры современных процессоров обычно невелики, но крупнейший в мире контрактный производитель полупроводников TSMC разрабатывает новый вариант своей технологии упаковки чипов CoWoS, с помощью которой можно будет создавать конструкции площадью до 9,5 размеров фотомаски 7885 мм² на подложках размером 120 × 150 мм 18 000 мм² . Производительность таких гигантов в 40 раз превысит показатели современных процессоров. Но и это не предел.

godnoTECH - Новости IT

TSMC представила прорыв: чипы станут в 40 раз мощнее. Intel и Samsung не успевают TSMC придумала технологию SoW-X: — Увеличивает мощность в 40 раз против нынешних моделей. — Позволяет ставить 60 блоков сверхбыстрой памяти HBM — как 60 спортивных двигателей в одном авто. — Запуск производства — 2027 год. До этого TSMC использовала технологию CoWoS: у неё 9.5x площадь, 12 блоков HBM. У SoW-X: 40x площадь + 60 HBM. godnoTECH - Новости IT

Техно Радар | Технологии, будущее, web3

TSMC наладит производство гигантских чипов — с киловаттной мощностью и в 40 раз быстрее современных Размеры современных процессоров обычно невелики, но крупнейший в мире контрактный производитель полупроводников TSMC разрабатывает новый вариант своей технологии упаковки чипов CoWoS, с помощью которой можно будет создавать конструкции площадью до 9,5 размеров фотомаски 7885 мм² на подложках размером 120 × 150 мм 18 000 мм² . Производительность таких гигантов в 40 раз превысит показатели современных процессоров. Но и это не предел. #tsmc #чиплеты #производствомикросхем

RUSmicro

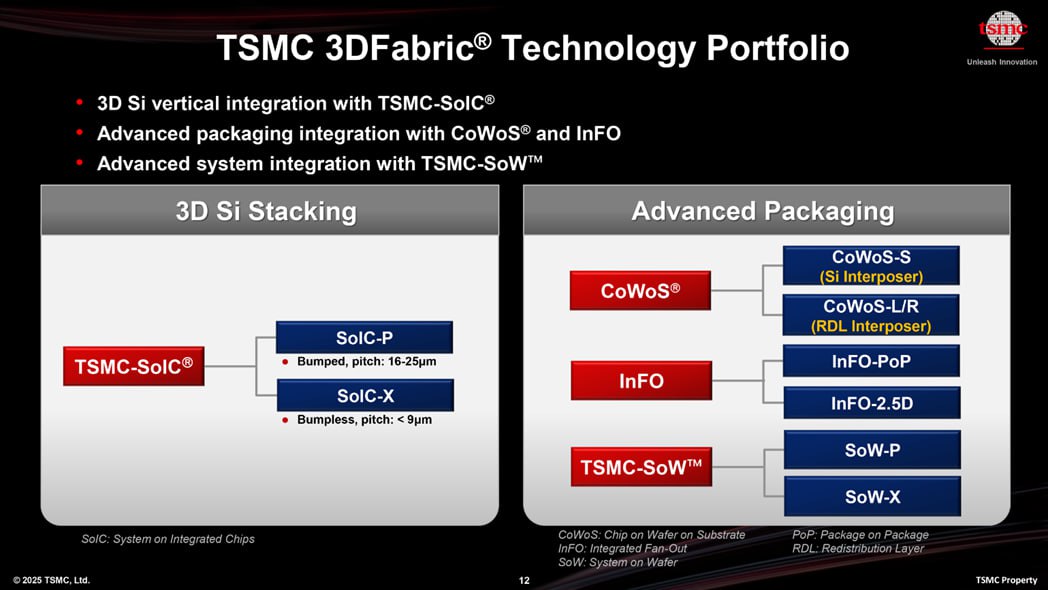

Подложки и пластины. Тренды. Тайвань В TSMC задумались над подложками киловаттных процессоров с производительностью в 40 раз большей, чем у привычных В TSMC в рамках усовершенствования технологии упаковки CoWoS задумались о переходе к многочиплетным сборкам на пластинах 120х150 мм 18 тыс кв мм . На них могут разместиться сборки площадью 7,885 тыс кв.мм . От таких сборок можно ожидать в 40 раз большей производительности, чем от привычных процессоров, уверены в компании. На Североамериканском технологическом симпозиуме TSMC представила свою новую дорожную карту 3DFabric, которая представляет масштабирование размеров интерпозеров далеко за пределы текущих ограничений. ..

RUSmicro

3 Для клиентов, которым требуется экстремальная производительность такие клиенты у TSMC есть , компания готова предложить еще одну технологию упаковки – System-on-Wafer SoW-X – система на пластине. Мы уже видели такие изделия – процессоры WFE Cerebras и Dojo Tesla, понятно, что будут и другие желающие получить экстремальную мощность от одного изделия, каким бы геометрически большим оно не было по текущим меркам. Хватило бы подводимого к стойкам электричества. И не только к стойкам. Ожидаемое энергопотребление – в сотнях ватт и более, выше киловатта. Это вновь требуется решать на системном уровне. TSMC собирается интегрировать монолитные ИС управления питанием PMIC с использованием TSV по технологии TSMC N16 FinFet и индукторы на пластине непосредственно в корпуса CoWoS-L с интерпозерами RDL, что должно позволить вести питание через подложку. Это сократит расстояние между источниками питания и активными кристаллами, снизит паразитные сопротивления. TSMC утверждает, что ее микросхемы управления мощностью на основе N16 легко справятся с высокоточной подачей и управлением напряжением DVS при требуемых уровнях тока, достигая в 5 раз большей плотности подачи мощности по сравнению с традиционными подходами. Кроме тогго, встроенные непосредственно в интерпозер или кремниевую подложку конденсаторы eDTC/DTC могут обеспечить хорошую до 2500 нФ/кв.мм стабильность питания за счет фильтрации колебаний напряжения в непосредственной близости от кристалла и обеспечения надежной работы даже при быстрых изменениях рабочей нагрузки. Этот подход обеспечивает эффективный DVS и улучшенный переходный отклик, что имеет решающее значение для управления энергоэффективностью в сложных многокристальных конструкциях. В целом, подход TSMC к подаче питания отражает сдвиг в направлении совместной оптимизации на системном уровне, где подача питания на кремний рассматривается как неотъемлемая часть «кремния», упаковки и конструкции системы, а не как отдельная функция каждого компонента. ..

Похожие новости

+1

+1

+2

+2

Qualcomm анонсировала новые процессоры Snapdragon 6 Gen 5 и 4 Gen 5 для улучшения производительности недорогих смартфонов

Технологии

1 день назад

Microsoft тестирует новую функцию для Windows 11, ускоряющую запуск приложений

Технологии

1 день назад

+1

+1

Павел Дуров анонсировал успех TON в стейкинге среди криптовалют

Экономика

1 день назад

Инвестиции в ИИ приводят к снижению свободного денежного потока у американских IT гигантов

Экономика

1 день назад

Мировые цены на продовольствие и электронику растут из-за войны в Иране

Экономика

21 час назад

+2

+2

Росатом и ФТС запускают проект по модернизации таможенной инфраструктуры с использованием ИИ

Политика

1 день назад